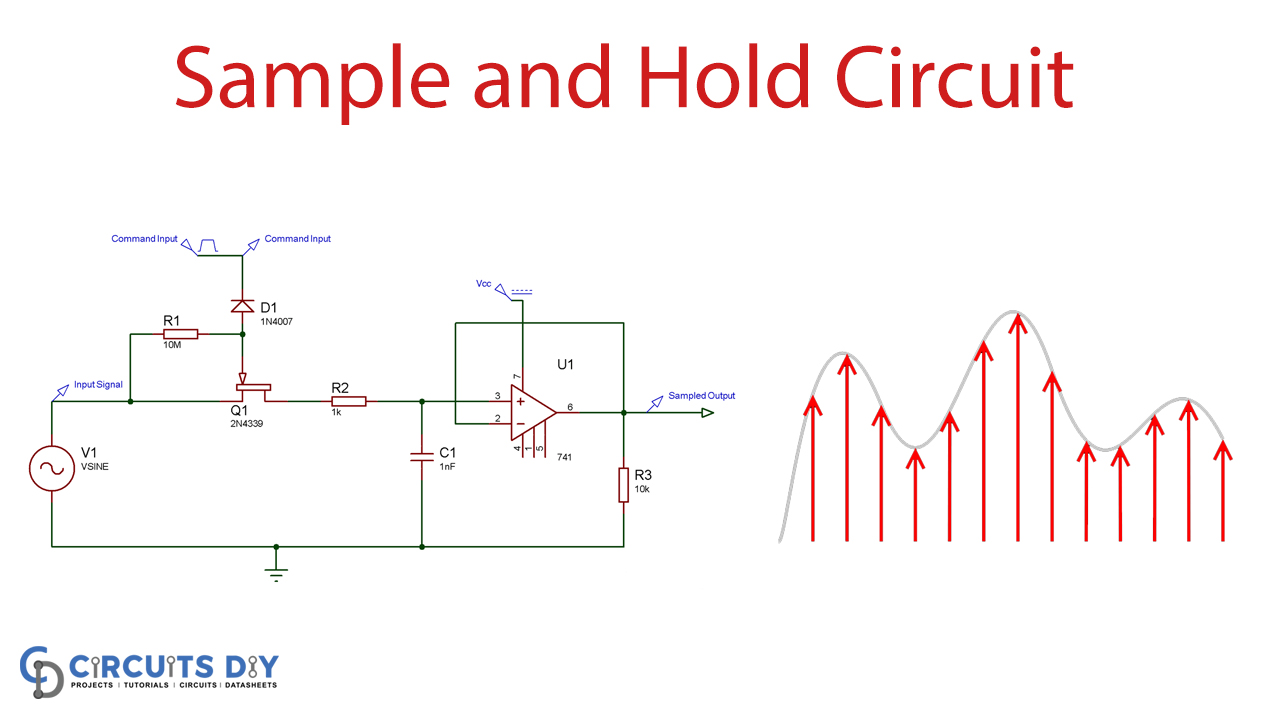

In this tutorial, we will construct the sample and hold circuit often; the Sample and Hold Circuit receives and keep samples of a set period from the analog input signal and then outputs the component input, which is sampled. This circuit is only useful to evaluate the input signal for a few microseconds.

A circuit sample and hold are built by switching sensors, couplers, and a functioning amplifier. The capacitor is the Sample and Hold Circuit’s backbone, although it keeps the input signal sampled and delivers it according to the command input at the output. This circuit is mainly used to exclude any change in input signal in analog to digital converters, which can corrupt the dependent variable.

Hardware Component

The following components are required to make the Sample and Hold Circuit

| S.no | Component | Value | Qty |

|---|---|---|---|

| 1. | Resistor | 1K, 10K, 10M | 1, 1, 1 |

| 2. | Diode | 1N4007 | 1 |

| 3. | Capacitor | 0.1uf | 1 |

| 4. | Analog Input and Pulse Input Generator | – | 1 |

| 5. | N-channel JFET | 2N4339 | 1 |

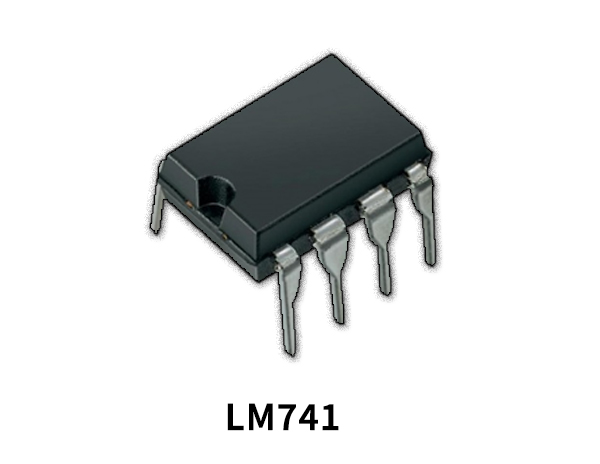

| 6. | Op-Amp IC | LM741 | 1 |

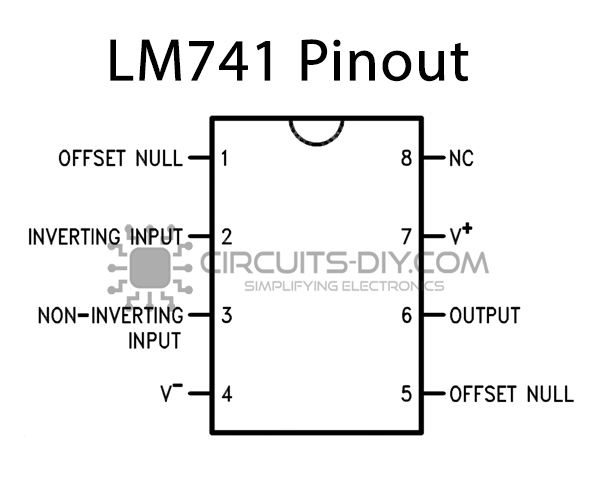

LM741 Pinout

For a detailed description of pinout, dimension features, and specifications download the datasheet of LM741

Sample and Hold Circuit

Working Explanation

You can use a 6-0-6 step-down transformer to furnish the analog signal at the input terminal. You could also use 555 Timer IC in astable mode with pulse or PWM input to the transistor. For Vcc to supply Op-amp IC, the range from +5 to +15V is also sufficient for us.

The transistor is regulated as an open switch when the command is LOW. The encapsulate transmitter is highly affected, making it very difficult to discharge and keep the load within a particular time. The holding period this time is known. And the flow rate at which the input signal is recorded is called the sampling period.

Applications and Uses

- ADCs (Conversion from Analog to Digital)

- Digital Conversion to analog (DACs)

- In the Analog Display

- Linear Systems

- In the system of data shipment

- In mathematical voltmeters

- Construction filters in signal