The P80C51 is a high-performance static 80C51 design fabricated with high-density CMOS technology with the operation from 2.7V to 5.5V. The P80C51 contains a 4k × 8 ROM, a 128 × 8 RAM, 32 I/O lines, three 16-bit counter/timers, a six-source, four-priority level nested interrupt structure, a serial I/O port for either multi-processor communications, I/O expansion or full-duplex UART, and on-chip oscillator and clock circuits.

In addition, the device is a low-power static design that offers a wide range of operating frequencies down to zero. Two software-selectable modes of power reduction—idle mode and power-down mode are available.

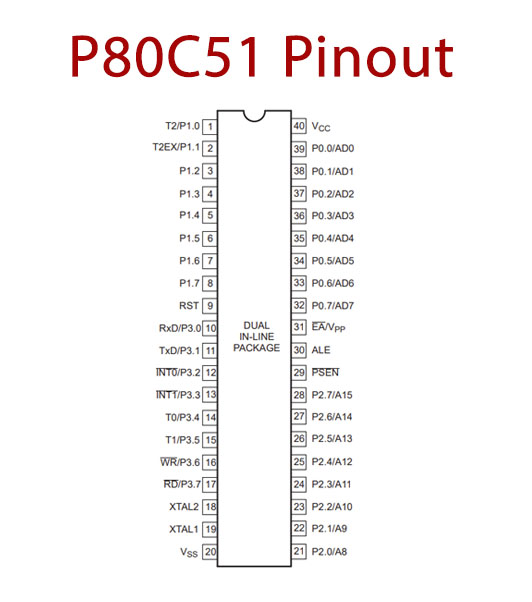

P80C51 Pinout

P80C51 Pin Configuration

| Pin Number | Pin Name | Description |

|---|---|---|

| 1-8 | P1.0-P1.7 | Port 1 |

| 9 | RST | Reset |

| 10 | P3.0/RXD | Port 3.0 / Serial Receive Pin |

| 11 | P3.1/TXD | Port 3.1 / Serial Transmit Pin |

| 12 | P3.2/INT0 | Port 3.2 / Interrupt 0 (Active Low) |

| 13 | P3.3/INT1 | Port 3.3 / Interrupt 1 (Active Low) |

| 14 | P3.4/T0 | Port 3.4 / Timer 0 |

| 15 | P3.5/T1 | Port 3.5 / Timer 1 |

| 16 | P3.6/WR | Port 3.6 / Write (Active Low) |

| 17 | P3.7/RD | Port 3.7 / Read (Active Low) |

| 18 | XTAL2 | Crystal Input |

| 19 | XTAL1 | Crystal Input |

| 20 | Vss | Ground |

| 21-28 | P2.0-P2.7 | Port 2 |

| 29 | PSEN | Program Store Enable (Active Low) |

| 30 | ALE | Address Latch Enable |

| 31 | EA | External Memory Enable (Active Low) |

| 32-39 | P0.7-P0.1 | Port 0 |

| 40 | Vcc | Positive Supply |

P80C51 Key Features

- 8051 Central Processing Unit

- 4k × 8 ROM (80C51)

- 128 × 8 RAM

- Three 16-bit counter/timers

- Boolean processor

- Full static operation

- Low voltage (2.7V to 5.5V 16MHz) operation

- Memory addressing capability

- 64k ROM and 64k RAM

- Power control modes:

- Clock can be stopped and resumed

- Idle mode

- Power-down mode

- CMOS and TTL compatible

- TWO speed ranges at VCC = 5V

- 0 to 16MHz

You can download this datasheet for P80C51 CPU with 128×8 RAM 4kBytes ROM and I/O – Datasheet from the link given below: