The 8031 CPU with 128×8 RAM and I/O controller is optimized for control applications. Byte-processing and numerical operations on small data structures are facilitated by a variety of fast addressing modes for accessing the internal. The instruction set provides a convenient menu of 8-bit arithmetic instructions, including multiply and divides Instructions.

The 8751H is an EPROM version of the 8051AH. It has 4 Kbytes of electrically programmable ROM which can be erased with ultraviolet light. It is fully compatible with the 8051AH but incorporates one additional feature Program Memory Security bit that can be used to protect the EPROM against unauthorized readout.

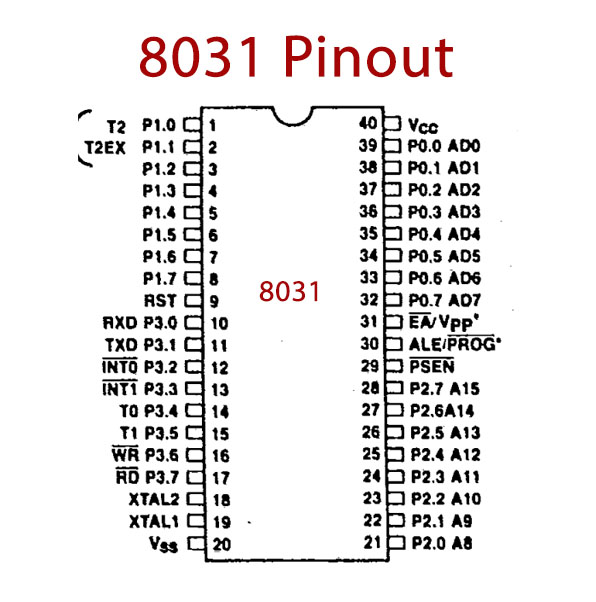

8031 Pinout

8031 Pin Configuration

| Pin No | Pin Name | Description |

| 1-8 | P1.0-P1.7 | Port 1 |

| 9 | RST | Reset |

| 10 | P3.0/RXD | Port 3.0 / Serial Receive Pin |

| 11 | P3.1/TXD | Port 3.1 / Serial Transmit Pin |

| 12 | P3.2/INT0 | Port 3.2 / Interrupt 0 (Active Low) |

| 13 | P3.3/INT1 | Port 3.3 / Interrupt 1 (Active Low) |

| 14 | P3.4/T0 | Port 3.4 / Timer 0 |

| 15 | P3.5/T1 | Port 3.5 / Timer 1 |

| 16 | P3.6/WR | Port 3.6 / Write (Active Low) |

| 17 | P3.7/RD | Port 3.7 / Read (Active Low) |

| 18 | XTAL2 | Crystal Input |

| 19 | XTAL1 | Crystal Input |

| 20 | Vss | Ground |

| 21-28 | P2.0-P2.7 | Port 2 |

| 29 | PSEN | Program Store Enable (Active Low) |

| 30 | ALE | Address Latch Enable |

| 31 | EA | External Memory Enable (Active Low) |

| 32-39 | P0.7-P0.1 | Port 0 |

| 40 | Vcc | Positive Supply |

8031 Key Features

- High Performance HMOS Process

- Internal Timers/Event Counters

- 2-Level Interrupt Priority Structure

- 32 1/O Lines (Four 8-Bit Ports)

- 64K External Program Memory Space

- Security Feature Protects EPROM Parts Against Software Piracy

- Boolean Processor

- Bit-Addressable RAM

- Programmable Full Duplex Serial Channel

Application

- Optimized for control applications.

You can download 8031 CPU with 128×8 RAM and I/O – Datasheet from the link given below: