Contents

hide

26LS33 is quadruple differential line receivers for balanced and unbalanced digital data transmission. The enable function is common to all four receivers and offers a choice of active-high or active-low input. The 3-state outputs permit connection directly to a bus-organized system. Fail-safe design ensures that, if the inputs are open, the outputs always are high.

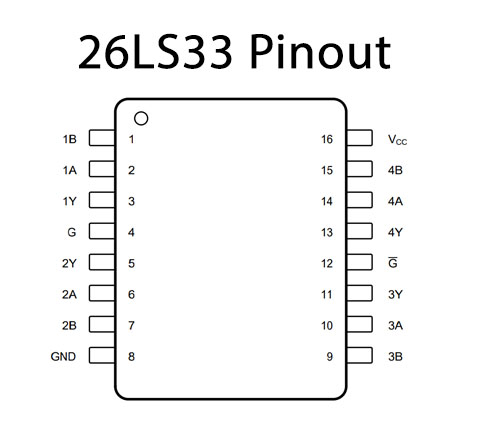

26LS33 Pinout

26LS33 Pin Configuration

| Pin No | Pin Name | Description |

|---|---|---|

| 1 | 1B | Input Pin 1B |

| 2 | 1A | Input Pin 1A |

| 3 | 1Y | Output Pin 1Y |

| 4 | G | Active-High select |

| 5 | 2Y | Output Pin 2Y |

| 6 | 2A | Input Pin 2A |

| 7 | 2B | Input Pin 2B |

| 8 | GND | Ground Pin |

| 9 | 3B | Input Pin 3B |

| 10 | 3A | Input Pin 3A |

| 11 | 3Y | Output Pin 3Y |

| 12 | G’ | Active-Low select |

| 13 | 4Y | Output Pin 4Y |

| 14 | 4A | Input Pin 4A |

| 15 | 4B | Input Pin 4B |

| 16 | VCC | Collector Supply Voltage |

26LS33 Key Features

- Input Hysteresis 50 mV Typical

- Operate From a Single 5-V Supply

- Low-Power Schottky Circuitry

- 3-State Outputs

- Complementary Output-Enable Inputs

- Input Impedance 12 kΩ Minimum

- Open Input Fail-Safe

Application

- High-Reliability Automotive Applications

- Factory Automation

- ATM and Cash Counters

- Smart Grids

- AC and Servo Motor Drives

You can download this datasheet for 26LS33 Quad Differential Line Receiver (O.C.) from the link given below: