Contents

hide

80C52 CPU with 256×8 RAM is a high-performance CMOS ROM, OTP, EPROM, and ROM are fewer versions of the 80C51 CMOS single-chip 8-bit microcontroller. The TS80C52 retains all features of the TEMIC 80C51 with extended ROM/EPROM capacity (8 Kbytes), 256 bytes of internal RAM, a 6-source, 4-level interrupt system, an on-chip oscillator, and three timer/ counters. In addition, the 80C52 has a dual data pointer, a more versatile serial channel that facilitates multiprocessor communication (EUART), and an X2 speed improvement mechanism.

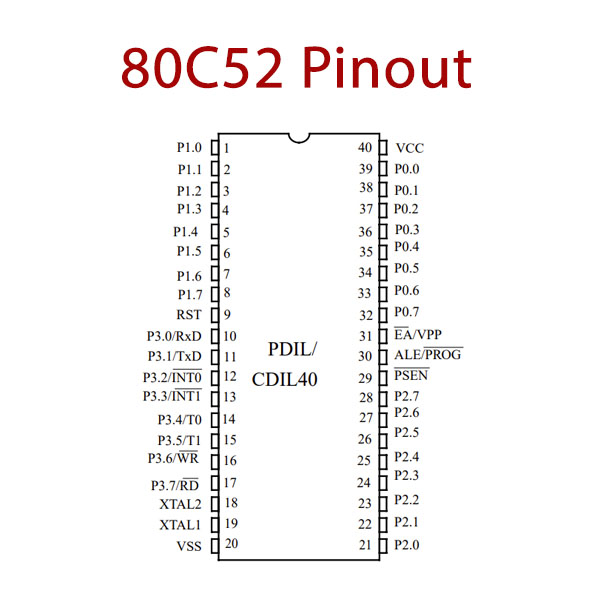

80C52 Pinout

80C52 Pin Configuration

| Pin Number | Pin Name | Description |

|---|---|---|

| 1-8 | P1.0-P1.7 | Port 1 |

| 9 | RST | Reset |

| 10 | P3.0/RXD | Port 3.0 / Serial Receive Pin |

| 11 | P3.1/TXD | Port 3.1 / Serial Transmit Pin |

| 12 | P3.2/INT0 | Port 3.2 / Interrupt 0 (Active Low) |

| 13 | P3.3/INT1 | Port 3.3 / Interrupt 1 (Active Low) |

| 14 | P3.4/T0 | Port 3.4 / Timer 0 |

| 15 | P3.5/T1 | Port 3.5 / Timer 1 |

| 16 | P3.6/WR | Port 3.6 / Write (Active Low) |

| 17 | P3.7/RD | Port 3.7 / Read (Active Low) |

| 18 | XTAL2 | Crystal Input |

| 19 | XTAL1 | Crystal Input |

| 20 | Vss | Ground |

| 21-28 | P2.0-P2.7 | Port 2 |

| 29 | PSEN | Program Store Enable (Active Low) |

| 30 | ALE | Address Latch Enable |

| 31 | EA | External Memory Enable (Active Low) |

| 32-39 | P0.7-P0.1 | Port 0 |

| 40 | Vcc | Positive Supply |

80C52 Key Features

- 8051 pin and instruction compatible

- Four 8-bit I/O ports

- Three 16-bit timer/counters

- 256 bytes scratchpad RAM

- Dual Data Pointer

- On-chip ROM/EPROM (8K-bytes)

- Programmable Clock Out and Up/Down Timer/ Counter 2

- Asynchronous port reset

You can download this datasheet for 80C52 CPU with 256×8 RAM – Datasheet from the link given below: