Contents

hide

80C32 CPU with 256×8 RAM is a high-performance CMOS version of the 8032 NMOS single-chip 8-bit µC. The fully static design of the 80C32 allows reducing system power consumption by bringing the clock frequency down to any value, even DC, without loss of data. The 80C32 retains all the features of the 8032: 8 K bytes of ROM; 256 bytes of RAM; 32 I/O lines; three 16 bit timers; a 6-source, 2-level interrupt structure; a full-duplex serial port; and on-chip oscillator and clock circuits.

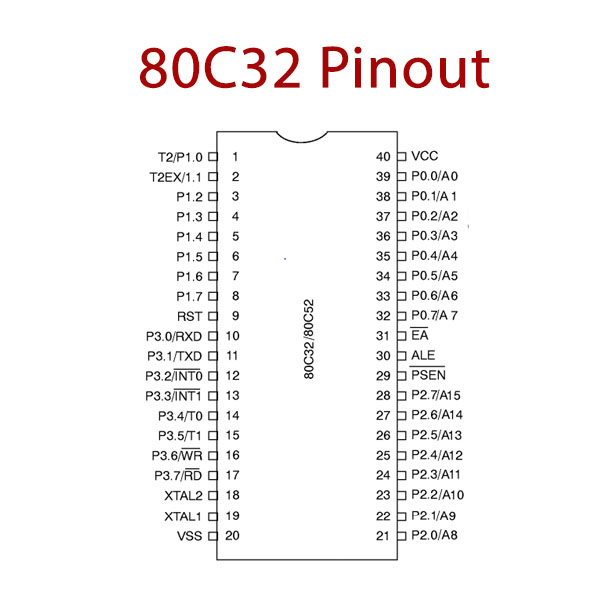

80C32 Pinout

80C32 Pin Configuration

| Pin Number | Pin Name | Description |

|---|---|---|

| 1-8 | P1.0-P1.7 | Port 1 |

| 9 | RST | Reset |

| 10 | P3.0/RXD | Port 3.0 / Serial Receive Pin |

| 11 | P3.1/TXD | Port 3.1 / Serial Transmit Pin |

| 12 | P3.2/INT0 | Port 3.2 / Interrupt 0 (Active Low) |

| 13 | P3.3/INT1 | Port 3.3 / Interrupt 1 (Active Low) |

| 14 | P3.4/T0 | Port 3.4 / Timer 0 |

| 15 | P3.5/T1 | Port 3.5 / Timer 1 |

| 16 | P3.6/WR | Port 3.6 / Write (Active Low) |

| 17 | P3.7/RD | Port 3.7 / Read (Active Low) |

| 18 | XTAL2 | Crystal Input |

| 19 | XTAL1 | Crystal Input |

| 20 | Vss | Ground |

| 21-28 | P2.0-P2.7 | Port 2 |

| 29 | PSEN | Program Store Enable (Active Low) |

| 30 | ALE | Address Latch Enable |

| 31 | EA | External Memory Enable (Active Low) |

| 32-39 | P0.7-P0.1 | Port 0 |

| 40 | Vcc | Positive Supply |

80C32 Key Features

- Power control modes

- 256 bytes of RAM

- 8 Kbytes of ROM (80C52)

- 32 programmable I/O lines

- Three 16 bit timer/counters

- 64 K program memory space

- 64 K data memory space

- Fully static design

- 0.8µ CMOS process

- Boolean processor

- 6 interrupt sources

- Programmable serial port

You can download this datasheet for 80C32 CPU with 256×8 RAM – Datasheet from the link given below: