The 74LS109 IC contains two independent J-K positive-edge-triggered flip-flops. It belongs to the 74XXYY IC series. The 74LS109 IC has a wide range of working voltage, a wide range of working conditions, and directly interfaces with CMOS, NMOS, and TTL. The IC 74LS109 is smaller in size and it has a much faster speed which makes it reliable in every kind of device.

What is a JK Flip-Flop?

The JK Flip Flop is basically a gated RS flip flop with the addition of the clock input circuitry. When both the inputs S and R are equal to logic “1”, the invalid condition takes place. Thus to prevent this invalid condition, a clock circuit is introduced. The JK Flip Flop has four possible input combinations because of the addition of the clocked input. The four inputs are “logic 1”, ‘logic 0”. “No change’ and “Toggle”.

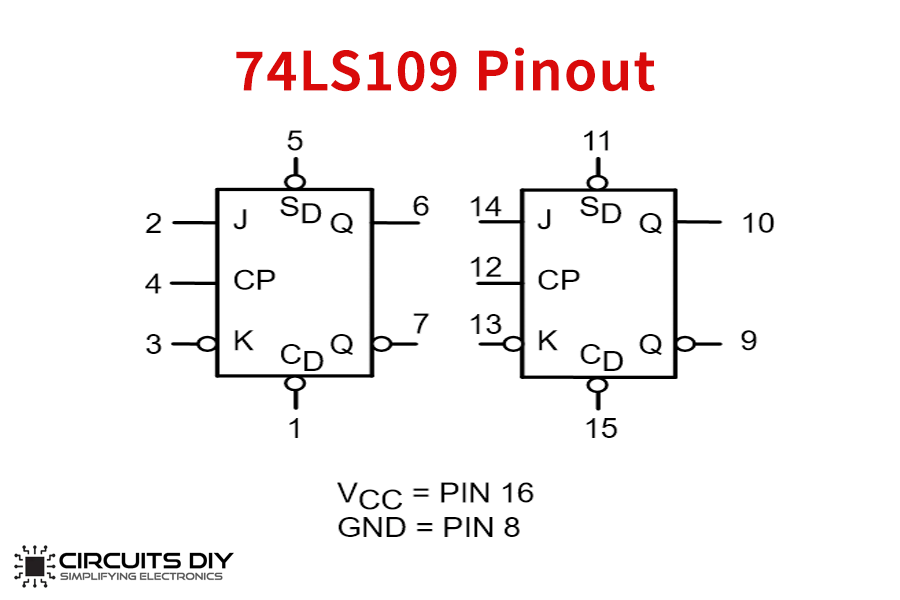

74LS109 Pinout

74LS109 Pin Configuration

| Pin No | Pin Name | Description |

|---|---|---|

| 1 | CLR1′ | Active low clear pin 1 |

| 2 | J1 | Input J1 |

| 3 | K1′ | Active low Input K1 |

| 4 | CLK1 | Clock Input 1 |

| 5 | 1PRE’ | Active low Preset pin 1 |

| 6 | 1Q | Active high output 1 |

| 7 | 1Q’ | Active low output 1 |

| 8 | GND | Ground pin |

| 9 | 2Q’ | Active low output 2 |

| 10 | 2Q | Active high output 2 |

| 11 | 2PRE’ | Active low Preset pin 2 |

| 12 | CLK2 | Clock Input 2 |

| 13 | K2′ | Active low Input K2 |

| 14 | J2 | Input J2 |

| 15 | CLR2′ | Active low clear pin 2 |

| 16 | Vcc | Chip Supply Voltage |

74LS109 Features & Specifications

- Technology Family: LS

- Triggering Edge: Positive

- Dual JK Flip Flop Package IC

- VCC (Min): 4.75V

- VCC (Max): 5.25

- Bits (#): 2

- Operating Voltage (Nom): 5V

- Frequency at normal voltage (Max): 35MHz

- Propagation delay (Max): 20ns

- IOL (Max): 8mA

- IOH (Max):-0.4mA

- Rating: Catalog

- Available in 14-pin PDIP, GDIP, PDSO packages

Applications

- Registers

- Counters

- Synchronizers

- Event Detectors

- Frequency Dividers

You can download this Datasheet for 74LS109 J-K Positive Edge Triggered Flip-Flop from the link given below:

See Also: 74LS56 50-to-1 Frequency Divider IC | 74LS14 Schmitt Trigger Hex Inverter IC | 74LS31 Hex Delay Element/Delay Line Generator

Comments are closed.