The 23K256 is a 256 Kbit Serial SRAM device. The memory is accessed via a simple Serial Peripheral Interface (SPI) compatible serial bus. The bus signals required are a clock input (SCK) plus separate data in (SI) and data out (SO) lines. Access to the device is controlled through a Chip Select (CS) input. Communication to the device can be paused via the hold pin (HOLD). While the device is paused, transitions on its inputs will be ignored, with the exception of Chip Select, allowing the host to service higher priority interrupts. The 23K256 is available in standard packages including 8-lead PDIP and SOIC, and advanced packaging including 8-lead TSSOP.

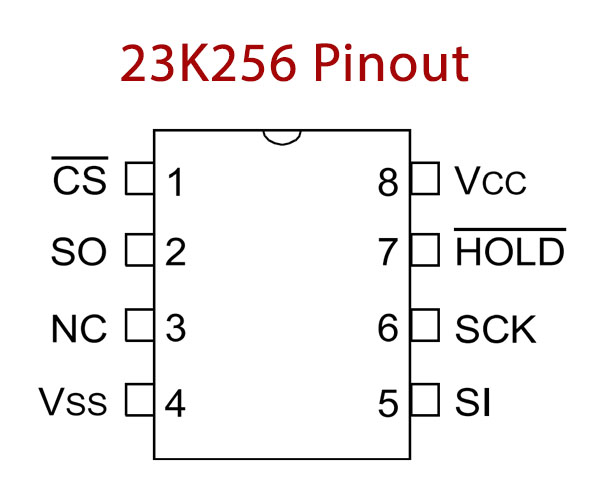

23K256 Pinout

23K256 Pin Configuration

| Pin No | Pin Name | Description |

|---|---|---|

| 1 | CS’ | Chip Select |

| 2 | SO | Serial Output Pin |

| 3 | NC | No Connection |

| 4 | VSS | Ground Pin |

| 5 | SI | Serial Input Pin |

| 6 | SCK | Serial Clock Pin |

| 7 | HOLD’ | Hold Pin |

| 8 | VCC | Power Supply Pin |

23K256 Key Feature

- Max. Clock 20 MHz

- Low-Power CMOS Technology:

- Read Current: 3 mA at 1 MHz

- Standby Current: 4 μA Max. at +85°C

- 32,768 x 8-bit Organization

- 32-Byte Page

- HOLD pin

- Flexible Operating modes:

- Byte read and write

- Page mode (32 Byte Page)

- Sequential mode

- Sequential Read/Write

- High Reliability

You can download this datasheet for 23K256 256k SPI Bus Serial SRAM – Datasheet from the link given below: